Description

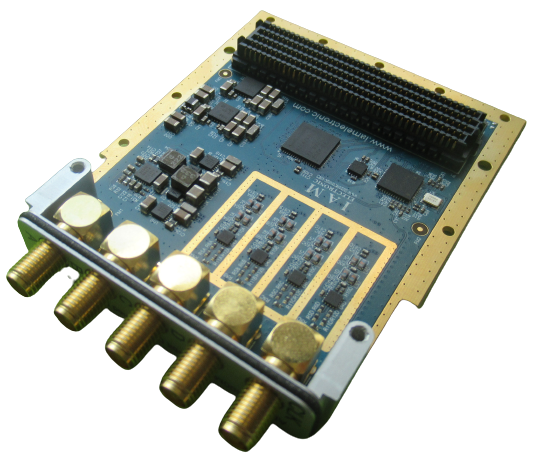

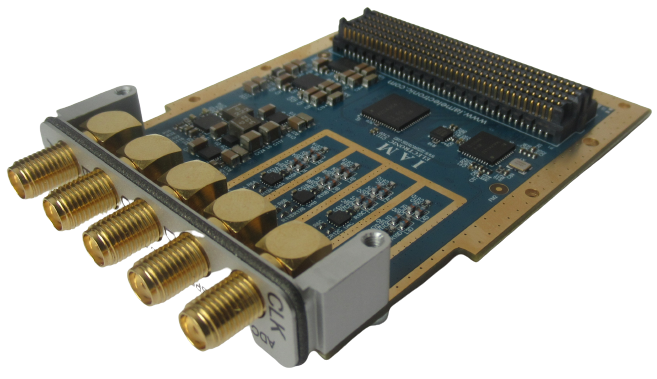

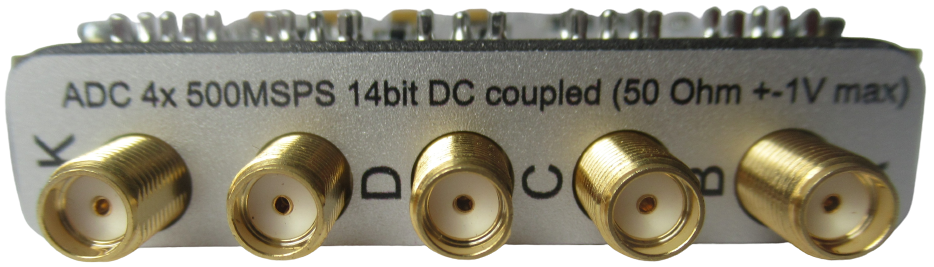

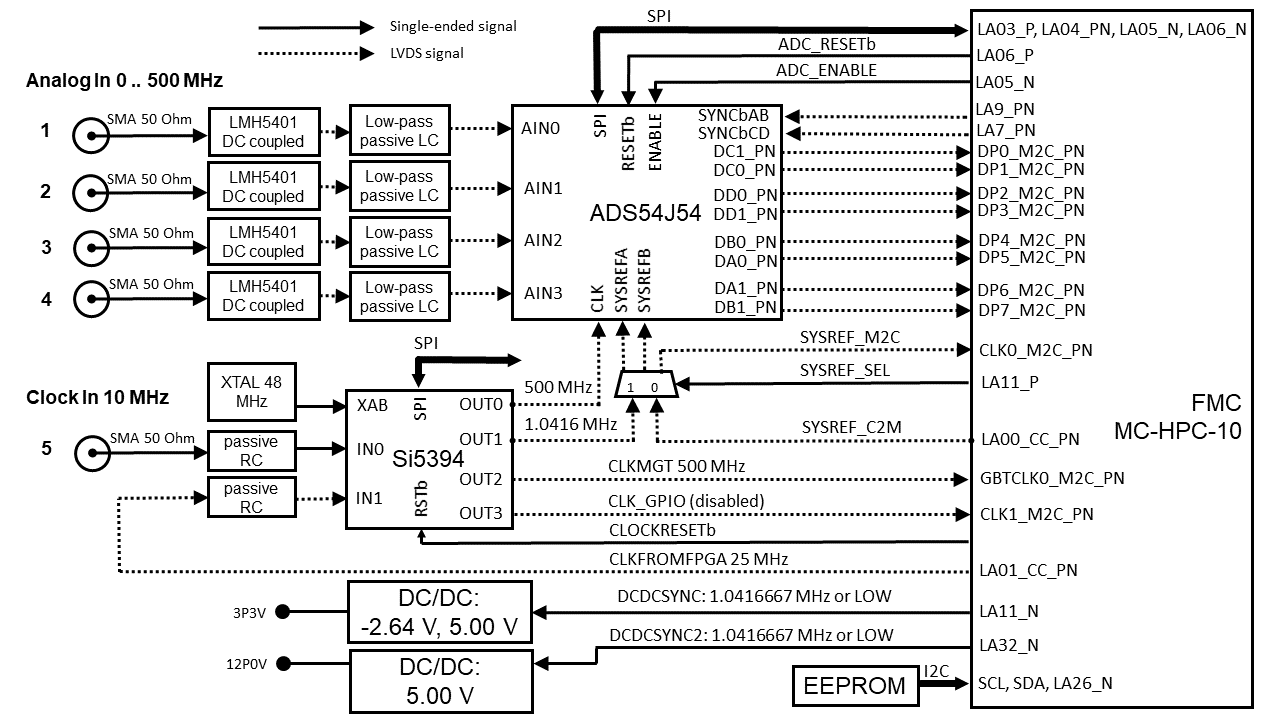

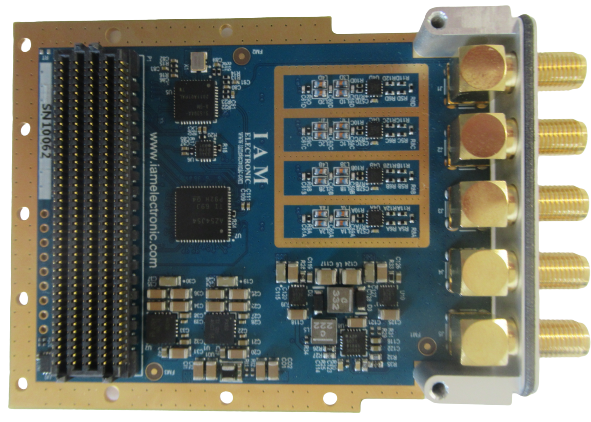

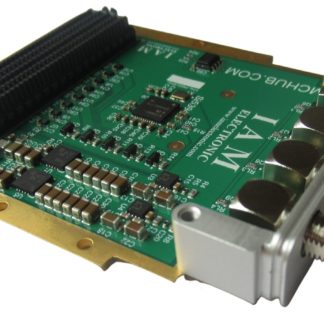

The FMC ADC 4x 500 MSPS 14 bit (DC coupled) is a 4-channel 500 MSPS 14 bit ADC card in FMC (FPGA Mezzanine Card, VITA 57.1) format using a High Pin-Count (HPC) connector. It was developed for the CERN Beam Instrumentation Group and is licensed under CERN Open Hardware Licence v2. The board has single-width, ruggedized, conduction cooled form factor and is fully ANSI VITA 57.1 compliant. The VADJ voltage must be 1.8 V, and the carrier must support data rates up to 5 Gbps for each JESD204B lane. With 2 lanes per ADC-channel, the maximum data rate is 40 Gbps (8 JESD204B lanes, 5 Gbps per ADC). Sampling and data clocks are generated by the Si5394A from Silicon Labs. This is a ultra-high-performance jitter attenuator for applications requiring the highest level of jitter performance. The device has an ultra-low jitter of 85 fs and can be quickly and easily configured using ClockBuilder Pro software.

Applications

- Beamline instrumentation

- Nuclear electronics

- Scientific instrumentation

- High-speed data acquisition

- Test and measurement instrumentation

- Digital Pulse Processing

- Research and education with FPGAs

Features

- High-pin count (HPC) connector

- 4 analog signal inputs

- DC-coupled, singled-ended 50 Ohm inputs

- +/- 500 mV analog input voltage range

- Bandwidth: DC to 500 MHz (or better)

- SNR: typ. 60 dB

- 500 MSPS sampling rate, 14 bit resolution, simultaneous sampling

- JESD204B data interface up to 5 Gbps lane rate (max. 8 lanes)

- SMA connector for external clock reference

- EEPROM for FRU information storage

- Open-source hardware

Online Wiki: CERN OHWR: FMC ADC 500M 14b 4cha